球栅陣列(BGA)封裝是目前FPGA和(hé)微處理(lǐ)器(qì)等各種高(gāo)度先進和(hé)複雜的半導體(tǐ)器(qì)件采用的标準封裝類型。用于嵌入式設計(jì)的BGA封裝技(jì)術(shù)在跟随芯片制(zhì)造商的技(jì)術(shù)發展而不斷進步,這類封裝一般分成标準和(hé)微型BGA兩種。這兩種類型封裝都要應對數(shù)量越來(lái)越多(duō)的I/O挑戰,這意味着信号迂回布線(Escape routing)越來(lái)越困難,即使對于經驗豐富的PCB和(hé)嵌入式設計(jì)師(shī)來(lái)說也極具挑戰性。

嵌入式設計(jì)師(shī)的首要任務是開(kāi)發合适的扇出策略,以方便電(diàn)路闆的制(zhì)造。在選擇正确的扇出/布線策略時(shí)需要重點考慮的因素有(yǒu):球間(jiān)距,觸點直徑,I/O引腳數(shù)量,過孔類型,焊盤尺寸,走線寬度和(hé)間(jiān)距,以及從BGA迂回出來(lái)所需的層數(shù)。

和(hé)嵌入式設計(jì)師(shī)總是要求使用最少(shǎo)的電(diàn)路闆層數(shù)。為(wèi)了降低(dī)成本,層數(shù)需要優化。但(dàn)有(yǒu)時(shí)設計(jì)師(shī)必須依賴某個(gè)層數(shù),比如為(wèi)了抑制(zhì)噪聲,實際布線層必須夾在兩個(gè)地平面層之間(jiān)。

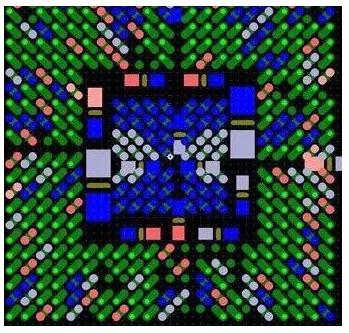

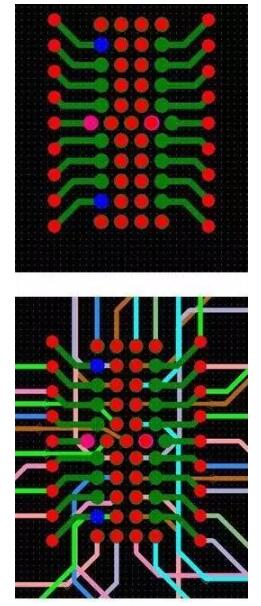

圖1:Dog bone型扇出

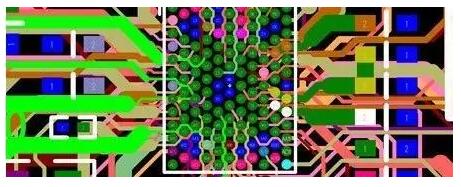

除了基于特定BGA的嵌入式設計(jì)固有(yǒu)的這些(xiē)設計(jì)因素外,設計(jì)的主要部分還(hái)包括嵌入式設計(jì)師(shī)從BGA正确迂回信号走線所必須采取的兩種基本方法:Dog bone型扇出(圖1)和(hé)焊盤內(nèi)過孔(圖2)。Dog bone型扇出用于球間(jiān)距為(wèi)0.5mm及以上(shàng)的BGA,而焊盤內(nèi)過孔用于球間(jiān)距在0.5mm以下(也稱為(wèi)超精細間(jiān)距)的BGA和(hé)微型BGA。間(jiān)距定義為(wèi)BGA的某個(gè)球中心與相鄰球中心之間(jiān)的距離。

圖2:焊盤內(nèi)過孔扇出方法

了解與這些(xiē)BGA信号布線技(jì)術(shù)有(yǒu)關的一些(xiē)基本術(shù)語很(hěn)重要。其中術(shù)語“過孔”是最重要的。過孔是指帶電(diàn)鍍孔的焊盤,這個(gè)電(diàn)鍍孔用于連接某個(gè)PCB層上(shàng)的銅線和(hé)另外一個(gè)層上(shàng)的銅線。高(gāo)密度多(duō)層電(diàn)路闆可(kě)能用到盲孔或埋孔,也稱為(wèi)微型過孔。盲孔隻有(yǒu)一面可(kě)見,埋孔兩面都不可(kě)見。

Dog bone型扇出

型BGA扇出法是分成4個(gè)象限,在BGA中間(jiān)則留出一個(gè)較寬的通(tōng)道(dào),用于布設從內(nèi)部出來(lái)的多(duō)條走線。分解來(lái)自BGA的信号并将它們連接到其它電(diàn)路涉及到多(duō)個(gè)關鍵步驟。

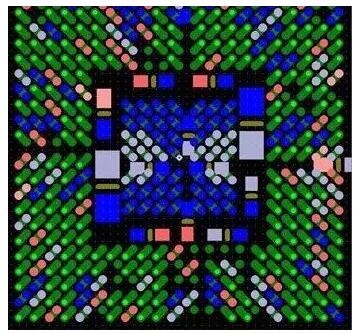

第一步是确定BGA扇出所需的過孔尺寸。過孔尺寸取決于許多(duō)因素:器(qì)件間(jiān)距,PCB厚度,以及需要從過孔的一個(gè)區(qū)域或一個(gè)周界布到另一個(gè)區(qū)域或另一個(gè)周界的走線數(shù)量。圖3顯示了與BGA有(yǒu)關的三個(gè)不同周界。周界是一個(gè)多(duō)邊形邊界,定義為(wèi)圍繞BGA球的一個(gè)矩陣或方形。

圖3:與BGA有(yǒu)關的三個(gè)不同周界。(Perimeter: 周界)

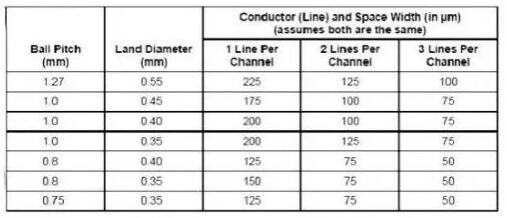

經過第一行(xíng)(水(shuǐ)平)和(hé)對應第一列(垂直)的虛線組成的是第一個(gè)周界,然後依次是第二個(gè)和(hé)第三個(gè)周界。設計(jì)師(shī)從BGA最外的周界開(kāi)始布線,然後不斷向裏走,直到BGA球最裏的周界。過孔尺寸用觸點直徑和(hé)球間(jiān)距計(jì)算(suàn),如表1所示。觸點直徑也是每個(gè)BGA球的焊盤直徑。

表1:使用觸點直徑和(hé)球間(jiān)距計(jì)算(suàn)過孔尺寸。(注:Ball pitch: 球間(jiān)距)

Land Diameter: 觸點直徑

conductor (Line) and space width(in μm): 導線(走線)和(hé)空(kōng)間(jiān)寬度(μm內(nèi))

Assumes both are the same: 假定兩者都相同

1 Line per channel: 每個(gè)通(tōng)道(dào)的1條走線

2 lines per channel: 每個(gè)通(tōng)道(dào)2條走線

一旦完成了Dog bone型扇出,并且确定了特定的過孔焊盤尺寸,第二步就是定義從BGA進入電(diàn)路闆內(nèi)層的走線寬度。确認走線寬度時(shí)要考慮許多(duō)因素。表1顯示了走線寬度。走線之間(jiān)要求的最小(xiǎo)空(kōng)間(jiān)限定了BGA迂回布線空(kōng)間(jiān)。重要的是要知道(dào),減小(xiǎo)走線之間(jiān)的空(kōng)間(jiān)将增加電(diàn)路闆制(zhì)造成本。

兩個(gè)過孔之間(jiān)的區(qū)域被稱為(wèi)走線通(tōng)道(dào)。相鄰過孔焊盤之間(jiān)的通(tōng)道(dào)面積是信号布線必須經過的最小(xiǎo)面積。表1用來(lái)計(jì)算(suàn)可(kě)以經過這個(gè)區(qū)域布線的走線數(shù)量。

如表1所示,實施BGA信号迂回布線時(shí)必須滿足走線寬度和(hé)走線間(jiān)最小(xiǎo)空(kōng)間(jiān)要求。相鄰過孔焊盤之間(jiān)的通(tōng)道(dào)面積是信号布線必須經過的最小(xiǎo)面積。

通(tōng)道(dào)面積CA=BGA間(jiān)距-d,其中d是過孔焊盤直徑。

可(kě)以經過這個(gè)區(qū)域布線的走線數(shù)量用表2進行(xíng)計(jì)算(suàn)。

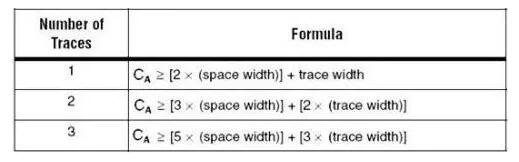

表2:計(jì)算(suàn)經過給定通(tōng)道(dào)面積的走線數(shù)量。(注:Number of Traces: 走線數(shù)量)

Formula: 公式;

Space width: 空(kōng)間(jiān)寬度;

Trace width: 走線寬度。

許多(duō)走線可(kě)以通(tōng)過不同通(tōng)道(dào)進行(xíng)布線。例如,如果BGA間(jiān)距不是十分精細,可(kě)以布1條或兩條走線,有(yǒu)時(shí)可(kě)以3條。比如對于1mm間(jiān)距的BGA來(lái)說,就可(kě)以布多(duō)條走線。然而,借助今天的先進PCB設計(jì),大(dà)多(duō)數(shù)時(shí)候一個(gè)通(tōng)道(dào)隻布一條走線。

一旦嵌入式設計(jì)師(shī)确定了走線寬度和(hé)間(jiān)距、經過一個(gè)通(tōng)道(dào)布線的走線數(shù)量以及用于BGA版圖設計(jì)的過孔類型,他或她就能估算(suàn)出所需的PCB層數(shù)。使用小(xiǎo)于最大(dà)值的I/O引腳數(shù)量可(kě)以減少(shǎo)層數(shù)。如果允許在第一層和(hé)第二層布線,那(nà)麽兩個(gè)外周界的布線就無需使用過孔。其它兩個(gè)周界可(kě)以在底層布線。

第三步,設計(jì)師(shī)需要根據要求保持阻抗匹配,并确定完全分解BGA信号要使用的布線層數(shù)量。接下來(lái)使用電(diàn)路闆頂層或放置BGA的那(nà)一層完成BGA外圈的布線。

剩下的內(nèi)部參數(shù)則分布在內(nèi)部布線層上(shàng)。根據每個(gè)通(tōng)道(dào)內(nèi)的內(nèi)部布線數(shù)量,需要公正地估計(jì)完成整個(gè)BGA布線所需的層數(shù)。

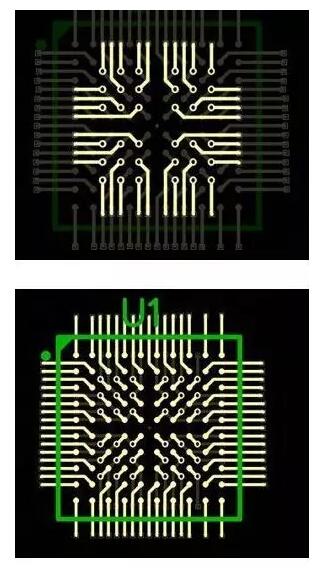

等外圈布線完了後,再布下一圈。圖4a和(hé)圖4b中的一組圖描述了PCB設計(jì)師(shī)如何布線不同的BGA圈,從最外面開(kāi)始,一直到中心。第一張圖顯示了第一和(hé)第二個(gè)內(nèi)圈是如何布線的。接着按同樣的方法布線後續的內(nèi)圈,直到完成全部的BGA布線。

圖4a和(hé)4b:如何布線不同的BGA圈,從最外層開(kāi)始,直到中心

在需要考慮電(diàn)磁幹擾(EMI)的一些(xiē)設計(jì)中,外層或頂層是不能用于布線的,即使外圈也不行(xíng)。在這種情況下,頂層用作(zuò)地平面。EMI包括了一個(gè)産品對于外界電(diàn)磁場(chǎng)的易感性,而外界電(diàn)磁場(chǎng)一般通(tōng)過耦合或輻射方式從一個(gè)産品進入另一個(gè)産品,并常常導緻後一個(gè)産品通(tōng)不過一緻性測試。産品隻有(yǒu)滿足以下三個(gè)标準才能認為(wèi)符合電(diàn)磁兼容規範要求:

不幹擾其它系統;

不受其它系統輻射的影(yǐng)響;

不會(huì)幹擾到本身。

為(wèi)了防止産品收發幹擾信号,建議對産品采取屏蔽措施。屏蔽一般是指用金屬外殼完全包裹住整個(gè)電(diàn)子産品或産品的一部分。然而,在大(dà)多(duō)數(shù)情況下将外層用地平面填充也可(kě)以起到屏蔽的作(zuò)用,因為(wèi)它能吸引能量,最大(dà)程度地減小(xiǎo)幹擾。

用于超細間(jiān)距的焊盤內(nèi)過孔技(jì)術(shù)

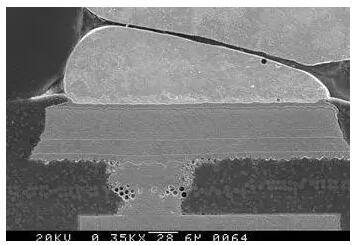

當使用焊盤內(nèi)過孔技(jì)術(shù)進行(xíng)BGA信号逃逸和(hé)布線時(shí),過孔直接放置在BGA焊盤上(shàng),并填充導電(diàn)材料(通(tōng)常是銀),并提供平坦的表面。

本文使用的微型BGA焊盤內(nèi)過孔扇出例子采用的是0.4mm球或引線間(jiān)距,PCB是18層,包括8個(gè)信号布線層。BGA布線通(tōng)常要求更多(duō)的層數(shù)。但(dàn)在這個(gè)例子中,層數(shù)不是問題,因為(wèi)隻用了少(shǎo)量的BGA球。關鍵問題仍然是微型BGA的0.4mm窄間(jiān)距,并且頂層除了扇出外不允許布線。目标是既做(zuò)到扇出微型BGA,又不負面影(yǐng)響PCB的制(zhì)造。

圖5顯示了BGA器(qì)件制(zhì)造商提供的外形圖。從圖中可(kě)以看到,推薦的焊盤尺寸是0.3mm(12mil),而引腳間(jiān)距是0.4mm(16mil)。由于焊盤之間(jiān)的間(jiān)距特别小(xiǎo),因此不可(kě)能實現傳統的Dog bone型扇出圖案。即使小(xiǎo)尺寸的過孔也無法用于Dog bone型扇出策略。這裏的小(xiǎo)尺寸過孔意思是6mil的鑽孔和(hé)10mil的環形焊盤。另外一個(gè)重要的機械性限制(zhì)是電(diàn)路闆厚度,本例是93mil。

圖5:BGA器(qì)件制(zhì)造商提供的外形圖

在這種情況下,最方便的解決方案是使用焊盤內(nèi)微過孔。然而,微過孔尺寸不能超過3mil。但(dàn)93mil的電(diàn)路闆厚度是一個(gè)限制(zhì)因素。另外一個(gè)選項是盲孔和(hé)埋孔技(jì)術(shù)。但(dàn)這些(xiē)選項将限制(zhì)制(zhì)造技(jì)術(shù)的選擇,并且會(huì)增加成本。

為(wèi)了能夠選擇不同的制(zhì)造公司,93mil厚的電(diàn)路闆中鑽孔尺寸不能小(xiǎo)于6mil,走線寬度不能小(xiǎo)于4mil。否則隻有(yǒu)少(shǎo)數(shù)高(gāo)端的電(diàn)路闆制(zhì)造商才能接手這個(gè)項目,而且價格不菲。圖6顯示了與本例有(yǒu)關的BGA外形圖。

圖6:這種扇出方法避免了使用高(gāo)端技(jì)術(shù),而且不會(huì)影(yǐng)響信号完整性。BGA引腳分成內(nèi)部引腳和(hé)外部引腳兩部分

圖6所示的扇出方法避免了使用高(gāo)端技(jì)術(shù),而且不影(yǐng)響信号完整性。BGA引腳被分成內(nèi)部和(hé)外部引腳兩個(gè)部分。焊盤內(nèi)過孔用于內(nèi)部,外部引腳在0.5mm栅格上(shàng)扇出。圖7a顯示的是頂層,圖7b顯示的是頂層和(hé)內(nèi)部布線層。

圖7a和(hé)7b:焊盤內(nèi)過孔用于內(nèi)部,而外部引腳在0.5mm栅格上(shàng)扇出。圖7a顯示的是頂層;圖7b顯示的是頂層和(hé)內(nèi)部布線層

由于BGA焊盤尺寸是0.3mm(12mil),間(jiān)距是0.4mm(16mil),因此焊盤內(nèi)使用了6/10mil的過孔(孔/環尺寸)。外部擴展扇出使用相同的過孔。在內(nèi)部,過孔之間(jiān)的間(jiān)隙是6mil,這是标準尺寸,不會(huì)引起制(zhì)造問題。外部的過孔間(jiān)隙是10mil。這個(gè)間(jiān)隙可(kě)以走一條3mil的線,線與過孔距離是3.34mil。這種特别的策略允許從0.4mm間(jiān)距微型BGA出來(lái)的所有(yǒu)信号都能成功扇出,而且不會(huì)提出任何特殊的制(zhì)造要求。

不管是使用Dog bone還(hái)是焊盤內(nèi)過孔方法,基本步驟是相同的,也就是先要确定正确的通(tōng)道(dào)空(kōng)間(jiān),包括定義過孔和(hé)焊盤的尺寸、走線寬度、阻抗要求和(hé)疊層。然而區(qū)别在于過孔安排和(hé)所用的過孔組。

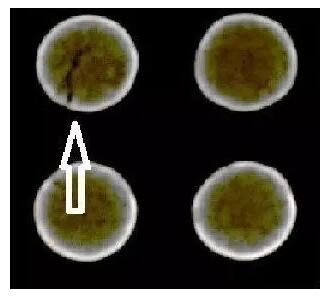

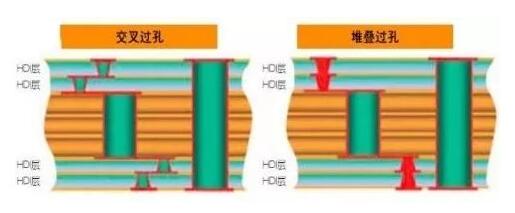

推薦使用深度最多(duō)6層的盲孔/埋孔配置。層數(shù)再多(duō)會(huì)引起制(zhì)造良率問題。優選技(jì)術(shù)是使用交叉過孔或堆疊過孔,如圖8所示。交叉過孔允許更加精确的注冊公差,因為(wèi)它們不像堆疊過孔那(nà)樣強制(zhì)要求完美對齊。

圖8:交叉過孔允許更大(dà)的注冊公差,因為(wèi)它們不像堆疊過孔那(nà)樣強制(zhì)要求完美對齊

沒有(yǒu)這些(xiē)步驟會(huì)出什麽錯

不管是用Dog bone還(hái)是焊盤內(nèi)過孔技(jì)術(shù),可(kě)制(zhì)造性和(hé)功能都是需要認真考慮的兩個(gè)重要方面。關鍵是要知道(dào)制(zhì)造工廠的制(zhì)造限制(zhì)。有(yǒu)些(xiē)工廠可(kě)以制(zhì)造特别嚴格的設計(jì)。然而,如果産品準備批量生(shēng)産,成本會(huì)很(hěn)高(gāo)。因此設計(jì)時(shí)就要考慮選用普通(tōng)制(zhì)造工廠特别重要。

總之,從制(zhì)造角度看要考慮的關鍵因素有(yǒu):

層疊

過孔-孔的大(dà)小(xiǎo)(取決于長寬比)

過孔-孔環 (要求最小(xiǎo)3mi)

過孔—堆疊(堆疊還(hái)是交叉)

銅箔到銅箔距離(推薦最小(xiǎo)3mil)

銅箔到鑽孔距離(要求最小(xiǎo)5mil)

用于裝配的BGA觸點尺寸與錫球尺寸

在可(kě)制(zhì)造性和(hé)功能方面總是存在折衷考慮。因此正确分析每個(gè)方面然後做(zuò)出合适的決定很(hěn)關鍵。

另一方面,功能包括了信号完整性、電(diàn)源分布和(hé)電(diàn)磁兼容。這些(xiē)可(kě)以分成以下幾個(gè)大(dà)類:

反射和(hé)傳輸線(一條線) 關鍵是阻抗控制(zhì)。阻抗由走線寬度、電(diàn)介質厚度和(hé)參考平面所控制(zhì)。

反射和(hé)傳輸線(一條線) 關鍵是阻抗控制(zhì)。阻抗由走線寬度、電(diàn)介質厚度和(hé)參考平面所控制(zhì)。

串擾(兩條或更多(duō)條線) 相同和(hé)相鄰層上(shàng)走線之間(jiān)的距離是控制(zhì)串擾的關鍵。每個(gè)信号層之間(jiān)放置地層、将對噪聲敏感的或輻射噪聲的走線周圍的屏蔽線接地有(yǒu)助于最大(dà)限度地減小(xiǎo)串擾。

電(diàn)源分布(軌破壞) 這是電(diàn)源網絡的電(diàn)感。使電(diàn)源和(hé)地平面相鄰并使用去耦電(diàn)容有(yǒu)助于控制(zhì)電(diàn)源浪湧。

電(diàn)磁幹擾(系統破壞) 控制(zhì)上(shàng)述所有(yǒu)單元,同時(shí)屏蔽整個(gè)PCB或對噪聲敏感和(hé)産生(shēng)噪聲的部分有(yǒu)助于控制(zhì)電(diàn)磁幹擾。

上(shàng)述措施對整個(gè)産品來(lái)說也是正确的。然而,在BGA區(qū)域尤其正确,因為(wèi)所有(yǒu)信号和(hé)電(diàn)源彼此靠得(de)很(hěn)近,因此極具挑戰性。對信号特性的正确了解有(yǒu)助于作(zuò)出在功能方面哪個(gè)網絡具有(yǒu)更高(gāo)優先級的決定。

在靠近BGA的層中使用大(dà)面積的接地平面有(yǒu)助于解決大(dà)多(duō)數(shù)信号完整性問題。盲孔的一個(gè)最大(dà)好處是,在盲孔/埋孔中消除了分支長度,這對高(gāo)頻信号來(lái)說尤其重要。

用于嵌入式設計(jì)的BGA封裝技(jì)術(shù)正在穩步前進,但(dàn)信号迂回布線仍有(yǒu)很(hěn)大(dà)難度,極具有(yǒu)挑戰性。在選擇正确的扇出/布線策略時(shí)需要考慮幾個(gè)關鍵因素:球間(jiān)距,觸點直徑,I/O引腳數(shù)量,過孔類型,焊盤尺寸,走線寬度和(hé)間(jiān)距以及疊層。遵循本文所述的一些(xiē)策略可(kě)以确保産品具有(yǒu)正确的形态、裝配和(hé)功能。